# International Journal of Computational Intelligence and Informatics, Vol. 3: No. 4, January - March 2014 Efficient Test Pattern Generator for BIST Using Multiple Single Input Change Vectors

D Punitha

Master of Engineering VLSI Design Sethu Institute of Technology Kariapatti, Tamilnadu, 626106 – India punithasuresh3555@gmail.com

#### S Ramkumar

Master of Engineering VLSI Design Sethu Institute of Technology Kariapatti, Tamilnadu, 626106 – India sraamu2k5@gmail.com

*Abstract*- Digital circuit's complexity and density are increasing while, at the same time, more quality and reliability are required. These trends, together with high test cost, make the validation of VLSI circuits more and more difficult. This paper proposes a novel test pattern generator (TPG) for built-in self-test. Our method generates multiple single input change (MSIC) vectors in a pattern, i.e., each vector applied to a scan chain is an SIC vector. According to the different scenarios of scan length, this paper develops two kinds of SIC generators to generate Johnson vectors and Johnson codeword's, i.e., the reconfigurable Johnson counter and the scalable SIC counter. The proposed TPG is flexible to both the test-per-clock and the test-per-scan schemes. A theory is also developed to represent and analyze the sequences and to extract a class of MSIC sequences. Analysis results have the favorable features of minimum transition of sequence, uniform distribution of pattern, uniqueness of pattern, and low hardware overhead. New seed generator circuit has to be developed to improve the fault coverage.

Keywords - BIST, SIC, TPG

# I. INTRODUCTION

A built-in self-test (BIST) is a mechanism that permits a machine to test itself. BIST techniques can effectively reduce the difficulty and complexity of VLSI testing, by introducing on-chip test hardware into the circuit-under-test (CUT). In conventional BIST architectures, the linear feedback shift register (LFSR) is commonly used in the test pattern generators (TPGs) and output response analyzers. A major drawback of these architectures is that the pseudorandom patterns generated by the LFSR lead to significantly high switching activities in the CUT [1], which can cause excessive power dissipation. They can also damage the circuit and reduce product yield and lifetime [2], [3]. In addition, the LFSR usually needs to generate very long pseudorandom sequences in order to achieve the target fault coverage in nanometer technology.

#### A. Existing method

Many advanced BIST techniques have been studied and applied. The first class is the LFSR tuning. Girard analyzed the impact of an LFSR's polynomial and seed selection on the CUT's switching activity, and proposed a method to select the LFSR seed for energy reduction [4]. The second class is low-power TPGs. One approach is to design low-transition TPGs. Wang and Gupta used two LFSRs of different speeds to control those inputs that have elevated transition densities [5]. Corno provided a low- power TPG based on the cellular automata to reduce the test power in combinational circuits [6]. Another approach focuses on modifying LFSRs. The scheme in [7] reduces the power in the CUT in general and clock tree in particular. In [8], a low-power BIST for data path architecture is proposed, which is circuit dependent. Bonhomme [9] used a clock gating technique where two non overlapping clocks control the odd and even scan cells of the scan chain so that the shift power dissipation is reduced by a factor of two. The ring generator [10] can generate a single-input change (SIC) sequence which can effectively reduce test power. The third approach aims to reduce the dynamic power dissipation during scan shift through gating of the outputs of a portion of the scan cells. Bhunia [11] inserted blocking logic into the stimulus path of the scan flip-flops to prevent the propagation of the scan ripple effect to logic gates. The need for transistors insertion, however, makes it difficult to use with standard cell libraries that do not have power-gated cells. In [12], the efficient selection of the most suitable subset of scan cells for gating along with their gating values is studied. The third class makes use of the prevention of pseudorandom patterns that do not have new fault detecting abilities [13], [14]. In [15], a pseudorandom BIST scheme was proposed to reduce switching activities in scan chains. Other approaches include LT-LFSR [16], a low-transition random TPG [17]. The TPG in [16] can reduce the transitions in the scan inputs by assigning the same value to most neighboring bits in the scan chain. In [17], power reduction is achieved by increasing the correlation between consecutive test patterns.

#### II. PROPOSED METHOD

This section develops a TPG scheme that can convert an SIC vector to unique low transition vectors for multiple scan chains. First, the SIC vector is decompressed to its multiple code words. Meanwhile, the generated code words will bit-XOR with a same seed vector in turn. Hence, a test pattern with similar test vectors will be applied to all scan chains. The proposed MSIC-TPG consists of an SIC generator, a seed generator, an XOR gate network, and a clock and control block. According to the different scenarios of scan length, this paper develops two kinds of SIC generators to generate Johnson vectors and Johnson code words, i.e., the reconfigurable Johnson counter

#### A. Test Pattern Generation Method

There are m primary inputs (PIs) and M scan chains in a full scan design, and each scan chain has l scan cells. The vector generated by an m-bit LFSR with the primitive polynomial can be expressed as  $S(t) = S_0(t)S_1(t)S_2(t), \ldots, S_{m-1}(t)$

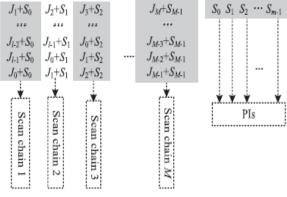

Figure 1. Symbolic representation of MSIC pattern

(hereinafter referred to as the seed), and the vector generated by an 1-bit Johnson counter can be expressed as J (t) =  $J_0(t)J_1(t)J_2(t), \ldots, J_{l-1}(t)$ . The first clock cycle, J =  $J_0 J_1 J_2, \ldots, J_{l-1}$  will bit-XOR with S =  $S_0S_1S_2, \ldots, S_{M-1}$ , and the results  $X_1X_{l+1}X_{2l+1}, \ldots, X_{(M-1)l+1}$  will be shifted into M scan chains, respectively. In the second clock cycle, J =  $J_0J_1 J_2, \ldots, J_{l-1}$  will be circularly shifted as J =  $J_{l-1} J_0 J_1, \ldots, J_{l-2}$ , which will also bit-XOR with the seed S =  $S_0S_1S_2, \ldots, S_{M-1}$ . The resulting  $X_2X_{l+2}X_{2l+2}...X_{(M-1)l+2}$  will be shifted into M scan chains, respectively. After 1 clocks, each scan chain will be fully loaded with a unique Johnson codeword, and seed  $S_0S_1S_2, \ldots, S_{M-1}$  will be applied to m PIs. Therefore circular Johnson counter can generate 1 unique Johnson code words through circular shifting a Johnson vector, the circular John son counter and XOR gates in Fig. 1 actually constitute a linear sequential de compressor.

### B. Reconfigurable Johnson Counter

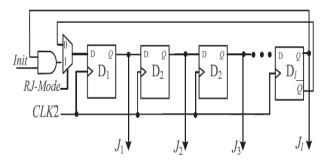

For a short scan length, we develop a reconfigurable Johnson counter to generate an SIC sequence in time domain. As shown in Fig.1, it can operate in three modes.

Figure 2. Reconfigurable Johnson counter

1) *Initialization:* When RJ\_Mode is set to 1 and *Init* is set to logic 0, the reconfigurable Johnson counter will be initialized to all zero states by clocking CLK2 more than l times.

2) Circular shift register mode: When RJ\_Mode and Init are set to logic 1, each stage of the Johnson counter will output a Johnson codeword by clocking CLK2 *l* times.

3) Normal mode: When RJ\_Mode is set to logic 0, the reconfigurable Johnson counter will generate 2*l* unique SIC vectors by clocking CLK2 2*l* times.

#### C. Scalable SIC counter

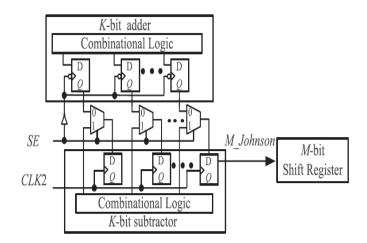

When the maximal scan chain length l is much larger than the scan chain number M, we develop an SIC counter named the "scalable SIC counter."

Figure 3. Scalable SIC counter

As shown in Fig. 3, it contains a k-bit adder clocked by the rising SE signal, a k-bit subtractor clocked by test clock CLK2, an M -bit shift register clocked by test clock CLK2, and k multiplexers. The value of k is the integer of log2(1-M). The k-bit adder is clocked by the falling SE signal, and generates a new count that is the number of 1s (0s) to fill into the shift register. As shown in figure. 3, it can operate in two modes.

1) If SE = 1 and the contents of the k-bit subtractor are not all zeros, M-Johnson will be kept at logic 1 (0).

2) Otherwise, it will be kept at logic0 (1). Thus the needed 1's (0s) will be shifted into the M-bit shift register by clocking CLK21 times, and unique Johnson code words will be applied into different scan chains.

#### D. Scan Chains

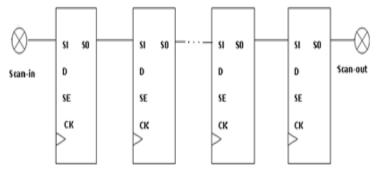

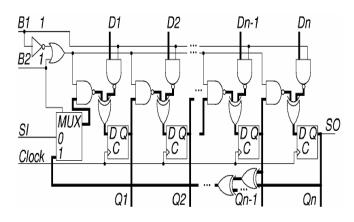

Figure 4. Scan Chain

Scan chains are the elements in scan-based designs that are used to shift-in and shift-out test data. A scan chain figure.4 is formed by a number of flip flops connected back to back in a chain with the output of one flip flop connected to another. The input of first flip flop is connected to the input pin of the chip (called scan-in) from where scan data is fed. The output of the last flip flop is connected to the output pin of the chip called (scan-out) which is used to take the shifted data out.

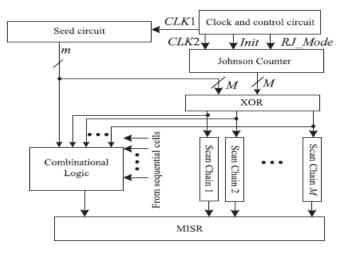

#### E. MISR

In test-per-scan scheme, the testing phase of the TPG fills the scan chains which will apply their contents to the circuit under test (CUT). All the scan outputs are connected to the multiple input signature register (MISR), which will perform signature compaction. The possibilities to speedup the test process by using multiple scan chains or by using a partial scan solution. It is shown in figure.5.

Figure 5. MISR

The proposed algorithm is to reduce the switching activity. In order to reduce the hardware overhead, the linear relations are selected with consecutive vectors or within a pattern, which can generate a sequence with a sequential de compressor, facilitating hardware implementation. Another requirement is that the MSIC sequence should not contain any repeated test patterns, because repeated patterns could prolong the test time and reduce test efficiency. Finally, uniformly distributed patterns are desired to reduce the test length i.e., number of patterns required to achieve a target fault coverage.

# III. MSIC SEQUENCES

The proposed algorithm is to reduce the switching activity. In order to reduce the hardware overhead, the linear relations are selected with consecutive vectors or within a pattern, which can generate a sequence with a sequential de-compressor, facilitating hardware implementation. Another requirement is that the MSIC sequence should not contain any repeated test patterns, because repeated patterns could prolong the test time and reduce test efficiency. Finally, uniformly distributed patterns are desired to reduce the test length i.e., number of patterns required to achieve a target fault coverage.

#### A. MSIC-TPGs for Test-per-Clock Schemes

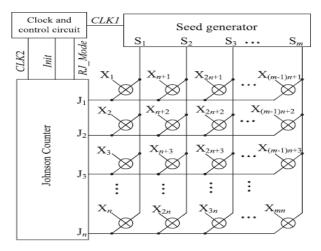

The MSIC-TPG for test-per-clock schemes is illustrated in figure. 6. The CUT's PIs  $X_1 - X_{mn}$  are arranged as an  $n \times m$  SRAM-like grid structure. Each grid has a two-input XOR gate whose inputs are tapped from a seed output and an output of the Johnson counter. The outputs of the XOR gates are applied to the CUT's PIs. A seed generator is an m-stage conventional LFSR, and operates at low frequency CLK1. The test procedure is as follows.

- 1) The seed generator generates a new seed by clocking CLK1 one time.

- 2) The Johnson counter generates a new vector by clocking CLK2 one time.

- 3) Repeat 2 until 21 Johnson vectors are generated.

- 4) Repeat 1–3 until the expected fault coverage or test length is achieved.

Figure 6. Test-Per-Clock

#### B. MSIC-TPG for test-per-scan schemes

The MSIC-TPG for test-per-scan schemes is illustrated in figure.7. The stage of the SIC generator is the same as the maximum scan length, and the width of a seed generator is not smaller than the scan chain number. The inputs of the XOR gates come from the seed generator and the SIC counter, and their outputs are applied to M scan chains, respectively. The output of the seed generator and XOR gates are applied to the CUT's PIs, respectively. The test procedure is as follows.

- 1) The seed circuit generates a new seed by clocking CLK1 one time.

- 2) RJ\_Mode is set to "0". The reconfigurable Johnson counter will operate in the Johnson counter mode and generate a Johnson vector by clocking CLK2 one time.

- 3) After a new Johnson vector is generated, RJ\_Mode and Init are set to 1. The reconfigurable Johnson counter operates as a circular shift register, and generates 1 code words by clocking CLK21 times. Then, a capture operation is inserted.

- 4) Repeat 2–3 until 21 Johnson vectors are generated.

- 5) Repeat 1–4 until the expected fault coverage or test length is achieved.

Figure 7. Test-Per-Scan scheme

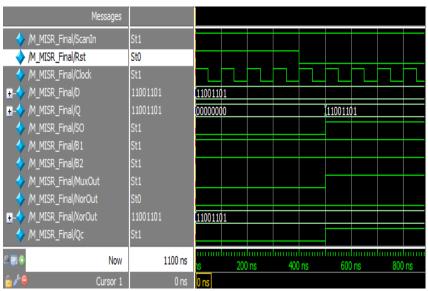

# IV. SIMULATION RESULTS

The proposed MSIC test pattern generator is designed using Verilog code and is stimulated by Model sim simulator. The simulated output for the proposed MSIC test pattern generator is shown below.

Figure 8. MISR

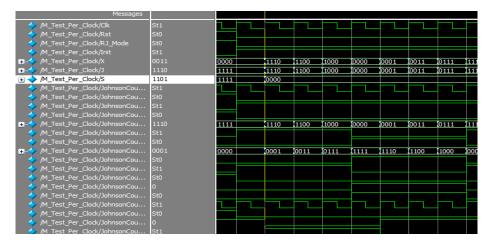

Figure 9. Test per clock(Johnson counter based)

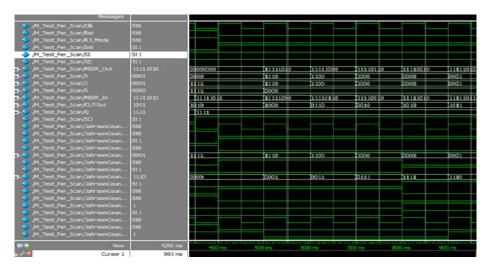

Figure 10. Test per scan (Johnson counter based)

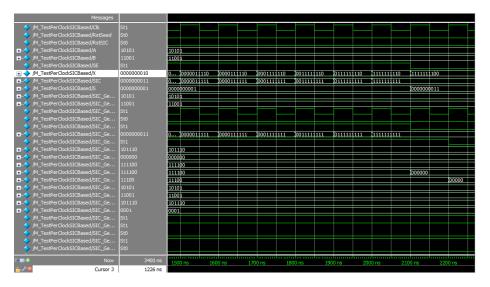

Figure 11. Test per clock (SIC based)

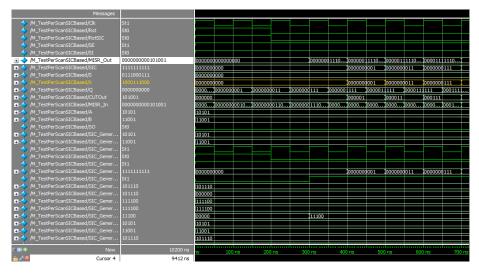

Figure 12. Test per scan (SIC based)

#### V. COMPARISON

Experiments on ISCAS'85 benchmarks and standard full-scan designs of ISCAS'89 benchmarks are conducted to analyze the performance of the proposed MSIC-TPG. The performance simulations are carried out with the Synopsys Design Analyzer and Prime Power. The area overheads of MSIC and LFSR are 21%–157% and 22%–258% respectively. The MSIC-TPG thus incurs less area overhead than the LFSR. The number of total equivalent gates is about 2309 for the conventional LFSR and 1089 for the MSIC-TPG. The MSIC-TPG saves 25%–50.0% total power and 15.6%–32.6% peak power against the conventional LFSR.

# VI. CONCLUSION

This paper has proposed a low-power test pattern generation method that could be easily implemented by hardware. It also developed a theory to express a sequence generated by linear sequential architectures, and extracted a class of SIC sequences named MSIC. Analysis results showed that an MSIC sequence had the favorable features of uniform distribution, low input transition density, and low dependency relationship between the test length and the TPG's initial states. Combined with the proposed reconfigurable Johnson counter or scalable SIC counter, the MSIC-TPG can be easily implemented, and is flexible to test-per-clock schemes and test-per-scan schemes. For a test-per-clock scheme, the MSIC-TPG applies SIC sequences to the CUT with the SRAM-like grid. For a test-per- scan scheme, the MSIC-TPG converts an SIC vector to low transition vectors for all scan chains. Experimental results and analysis results demonstrate that the MSIC-TPG is scalable to scan length, and has negligible impact on the test overhead. After the generating the MSIC, in this we conduct the validation process on the combinational logic circuit and verified the output.

# References

- Y. Zorian, "A distributed BIST control scheme for complex VLSI devices", in 11th Annual. IEEE VLSI Test Symposium Digital. Papers, pp. 4–9, Apr. 1993.

- P. Girard, "Survey of low-power testing of VLSI circuits", IEEE Design Test Computation, vol. 19, no. 3, pp. 80–90, May–Jun. 2002.

- [3] A. Abu-Issa and S. Quigley, "Bit-swapping LFSR and scan-chain ordering: A novel technique for peak- and average-power reduction in scan-based BIST", IEEE Transactions Computer.-Aided Design Integr. Circuits Syst., vol. 28, no. 5, pp. 755–759, May 2009.

- [4] P. Girard, L. Guiller, C. Landrault, S. Pravossoudovitch, J. Figueras, S. Manich, P. Teixeira, and M. Santos, "Lowenergy BIST design: Impact of the LFSR TPG parameters on the weighted switching activity", in Proc. IEEE Int. Symposium Circuits System, vol. 1, pp. 110–113, Jul. 1999.

- [5] S. Wang and S. Gupta, "DS-LFSR: A BIST TPG for low switching activity", IEEE Transactions Computer.-Aided Design Integr. Circuits Systems, vol. 21, no. 7, pp. 842–851, Jul. 2002.

- [6] F. Corno, M. Rebaudengo, M. Reorda, G. Squillero, and M. Violante, "Low power BIST via non-linear hybrid cellular automata", Proceedings 18th IEEE VLSI Test Symposium, pp.29–34, Apr.-May 2000.

- [7] P. Girard, L. Guiller, C. Landrault, S. Pravossoudovitch, and H. Wun- derlich, "A modified clock scheme for a low power BIST test pattern generator", Proceedings 19th IEEE VTS VLSI Test Symposium, pp. 306–311, Mar.–Apr. 2001.

- [8] D. Gizopoulos, N. Krantitis, A. Paschalis, M. Psarakis, and Y. Zorian, "Low power/energy BIST scheme for datapaths", in Proc. 18th IEEE VLSI Test Symposium, pp. 23–28, Apr.–May 2000.

- [9] Y. Bonhomme, P. Girard, L. Guiller, C. Landrault, and S.Pravos- soudovitch, "A gated clock scheme for low power scan testing of logic ICs or embedded cores", Proceedings 10th Asian Test Symposium, pp.253–258, Nov. 2001.

- [10] C. Laoudias and D. Nikolos, "A new test pattern generator for high defect coverage in a BIST environment", Proceedings 14th ACM Great Lakes Symposium. VLSI, pp. 417–420, Apr. 2004.

- [11] S. Bhunia, H. Mahmoodi, D. Ghosh, S. Mukhopadhyay, and K. Roy, "Low-power scan design using first-level supply gating", IEEE Transactions Very Large Scale Integr.(VLSI) Systems, vol. 13, no. 3, pp. 384–395, Mar.2005.

- [12] X. Kavousianos, D. Bakalis, and D. Nikolos, "Efficient partial scan cell gating for low-power scan-based testing", ACM Transactions. Design Autom. Electron. Systems, vol.14, no. 2, pp. 28-1–28-15, Mar. 2009.

- [13] P. Girard, L. Guiller, C. Landrault, and S.Pravossoudovitch, "A test vector inhibiting technique for low energy BIST design", in Proceedings 17th IEEE VLSI Test Symposium, pp. 407–412, Apr. 1999.

- [14] S. Manich, A. Gabarro, M. Lopez, J. Figueras, P. Girard, L. Guiller, C. Landrault, S. Pravossoudovitch, P. Teixeira, and M. Santos, "Low power BIST by filtering non-detecting vectors", J. Electron. Test.-Theory Application., vol.16, no. 3, pp. 193–202, Jun. 2000.

- [15] N. Basturkmen, S. Reddy, and I. Pomeranz, "A low power pseudo- random BIST technique", Proceedings IEEE International Conference, Computer Design: VLSI Computer Process, pp. 468–473, Sep. 2002.

- [16] S. Wang and S. Gupta, "LT-RTPG: A new test-per-scan BIST TPG for low switching activity", IEEE Transactions. Computer.-Aided Design Integr. Circuits Systems., vol. 25, no. 8, pp. 1565–1574, Aug. 2006.

- [17] M. Nourani, M. Tehranipoor, and N. Ahmed, "Low-transition test pattern generation for BIST-based applications", IEEE Transactions Computations, vol. 57, no. 3, pp. 303–315, Mar. 2008.